# GY3282 ARINC 429 总线接口电路

## 1 概述

GY3282 是一款高性能 CMOS ARINC 429 总线接口电路, 满足 ARINC 429 规范要求的编码和时分复用串行数据协议。

GY3282 包括独立工作的两个接收器和一个发送器,两个接收器以 10 倍的接收数据速率频率工作,该频率可以与发送器的数据速率相同或不同。虽然两个接收器工作的频率相同,但它们在功能上是独立的,每个接收器都异步接收串行数据。该发送器部分主要由 FIFO 和时序电路组成。FIFO 用于缓存多达 8 个ARINC 数据字,以用于串行传输。时序电路用于根据 ARINC 429 的要求正确地分离每个 ARINC 字。即使 ARINC 429 规定了 32bit 的字(包括奇偶校验),GY3282 也可以通过编程支持字长为 25bit 的字。接收器对所接收的数据字要进行奇偶校验,并将奇偶校验结果存储在接收锁存器中,在第一个接收数据字被校验的期间,输出到引脚 BD08 上(逻辑"0"表示接收并存储逻辑"1"的数量为奇数;逻辑"1"表示接收并存储逻辑"1"的数量为偶数)。在发送器中,奇偶校验位生成电路将根据 PARCK 控制信号的状态产生奇偶校验位。BD12 上的逻辑"0"将在输出数据流中产生一个奇校验位。

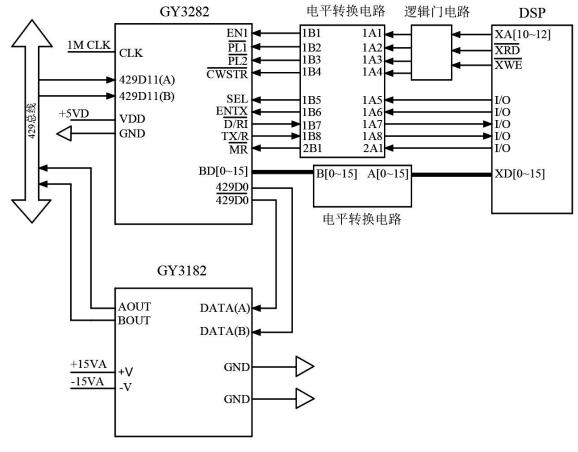

GY3282 是 5V 电源供电,完全保证在电压范围内(5V±5%)和全军用温度范围内支持 ARINC 429 的数据速率。支持 UL、CMOS 或 NMOS 电路系统。GY3282 的发送器和接收器的数据速率可以是 0 到 100Kbits。外部时钟必须是数据速率的十倍,以确保数据唯一。通常情况下,该器件与 GY3182(满足 ARINC 429 的规格单片 DI 双极差分线路驱动器)配对使用。

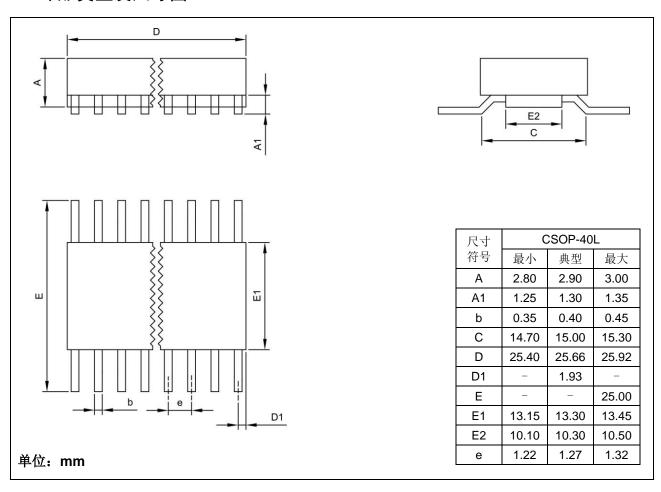

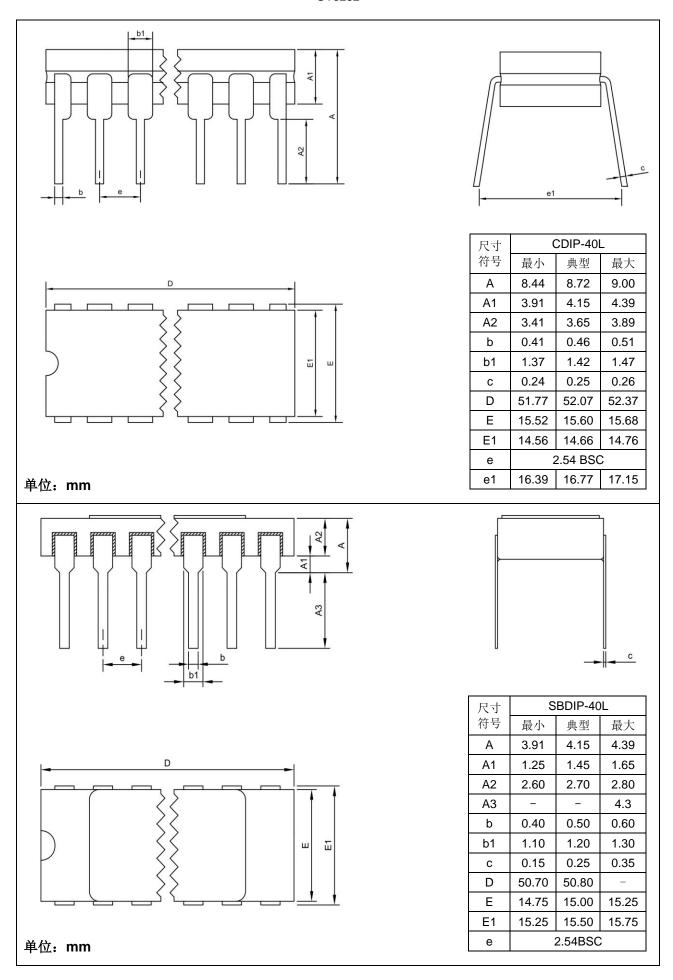

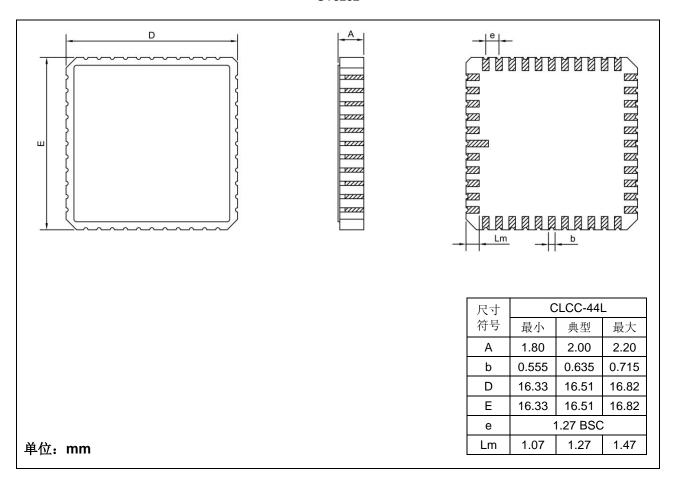

GY3282 提供 40 管脚 CDIP、SBDIP、CSOP 以及 44 管脚 CLCC 封装形式,电路电气特性兼容 INTERSIL 公司的 HS-3282 和 HOLT 公司的 HI-3282。

## 2 特性说明

- ARINC 429 兼容

- 100Kbits 或 12.5Kbits 数据速率, 25bits 或 32bits 字长

- 独立的接收器和发送器

- 两路独立工作的接收器,可直接连接 ARINC 总线

- 接收数据串行到并行转换

- 发送数据并行到串行转换

- 接收数据进行奇偶校验

- 生成发送数据的奇偶校验

- 自动字间隔计时器

- 单 5V 电源供电

- 低功耗

- 符合军用级工作温度标准(-55°C~+125°C)

# 3 技术说明

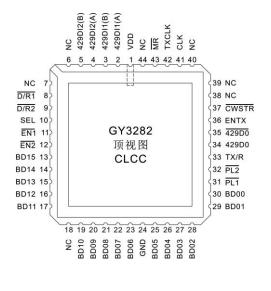

## 3.1 引脚图

图 1 CDIP、SBDIP、CSOP 顶视图

图 2 CLCC 顶视图

## 3.2 引出端功能

GY3282 引出端功能

| 引脚序号 |                       |                                                          |      |                                         |

|------|-----------------------|----------------------------------------------------------|------|-----------------------------------------|

| CLCC | CDIP<br>SBDIP<br>CSOP | 符号                                                       | 引脚方向 | 功能描述                                    |

| 1    | 1                     | $V_{DD}$                                                 | 输入   | 电源                                      |

| 2    | 2                     | 429 DI1 (A)                                              | 输入   | 接收通道 1 的 ARINC 429 的数据输入                |

| 3    | 3                     | 429 DI1 (B)                                              | 输入   | 接收通道 1 的 ARINC 429 的数据输入                |

| 4    | 4                     | 429 DI2 (A)                                              | 输入   | 接收通道 2 的 ARINC 429 的数据输入                |

| 5    | 5                     | 429 DI2 (B)                                              | 输入   | 接收通道 2 的 ARINC 429 的数据输入                |

| 6    | -                     | NC                                                       | -    | 不连接                                     |

| 7    | -                     | D/R1     輸出     以读取       B     接收通道 2 输出就绪标志: 表示一个有效以读取 |      | 不连接                                     |

| 8    | 6                     |                                                          |      | 接收通道 1 输出就绪标志:表示一个有效的数据字是随时可以读取         |

| 9    | 7                     |                                                          |      | 接收通道 2 输出就绪标志:表示一个有效的数据字是随时可以读取         |

| 10   | 8                     |                                                          |      | 总线数据选择器输入:用于从接收器 1 或接收器 2 中选择一个 16 位数据字 |

| 11   | 9                     | EN1                                                      | 输入   | 接收通道 1 的数据到数据总线的使能信号,低电平有效              |

| 12   | 10                    | 11 BD15 输入输出 双向数据总线: 用于从接收器获取 送器存储器或控制字寄存器。              |      | 接收通道2的数据到数据总线的使能信号,低电平有效                |

| 13   | 11                    |                                                          |      | 双向数据总线:用于从接收器获取数据,或将数据加载到发送器存储器或控制字寄存器。 |

| 14   | 12                    |                                                          |      | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC)  |

| CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 引脚序号 |       |       |      |                                        |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------|----------------------------------------|--|--|

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CLCC | SBDIP | 符号    | 引脚方向 | 功能描述                                   |  |  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15   | 13    | BD13  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16   | 14    | BD12  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17   | 15    | BD11  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18   | _     | NC    | -    | 不连接                                    |  |  |

| 21         18         BD08         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC)           22         19         BD07         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC)           23         20         BD06         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC)           24         21         GND         输入         地           25         22         BD05         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字音存器           26         23         BD04         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字音存器           27         24         BD03         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字音存器           28         25         BD02         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字音存器           30         27         BD00         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字音存器           31         28         PL1         输入         并行加载输入信号: 加载第二个 16bit 字到发送器存储器           32         29         PL2         输入         并行加载输入信号: 加载第二个 16bit 字到发送器存储器           33         30         TXR         输出         发送器输出或第二个 16bit 字到发送器存储器           34         1         429DO         输出                                                                                                                                                                                                          | 19   | 16    | BD10  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 22         19         BD07         输入输出         参見Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC)           23         20         BD06         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC)           24         21         GND         输入         地           25         22         BD05         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           26         23         BD04         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           27         24         BD03         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           28         25         BD02         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           29         26         BD01         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           30         27         BD00         输入输出         参见Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到报户字寄存器           31         28         PL1         输入         并行加载输入信号: 加载第二个 16bit 字到发送器存储器           32         29         PL2         输入         并行加载输入信号: 加载第二个 16bit 字到发送器存储器, 并启动数据产生的营业或 2000 编出           33         30         TXR         输出         发送署数据输出           34         31         429DO         输出 </td <td>20</td> <td>17</td> <td>BD09</td> <td>输入输出</td> <td>参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC)</td>                                                                                     | 20   | 17    | BD09  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 23         20         BD06         输入输出         参见 Pin11(CDIP, SBDIP, CSOP)或 Pin13(CLCC)           24         21         GND         输入         地           25         22         BD05         输入输出         参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC)           26         23         BD04         输入输出         参见 Pin11(CDIP, SBDIP, CSOP)或 Pin13(CLCC),不能被人支援到约约约时产商子器           27         24         BD03         输入输出         参见 Pin11(CDIP, SBDIP, CSOP)或 Pin13(CLCC),不能被人支援到约约约时产商子器           28         25         BD02         输入输出         参见 Pin11(CDIP, SBDIP, CSOP)或 Pin13(CLCC),不能被人支援到约约约中产商子器           29         26         BD01         输入输出         参见 Pin11(CDIP, SBDIP, CSOP)或 Pin13(CLCC),不能被人支援到约约约中产商子器           30         27         BD00         输入输出         参见 Pin11(CDIP, SBDIP, CSOP)或 Pin13(CLCC),不能裁人支援到约约约中产商子器           31         28         PL1         输入         并行加载输入信号,加载第一个 16bit 宁到发送器存储器           32         29         PL2         输入         并行加载输入信号,加载第二个 16bit 宁到发送器存储器           33         30         TX/R         输出         发送器输出债额的信器进程中           34         31         429DO         输出         发送器输出债额的信器进税           35         32         429DO         输出         发送器有价额分别           36                                                                                                                                                                                                                                         | 21   | 18    | BD08  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 24         21         GND         输入         地           25         22         BD05         输入输出         参见 Pin11 (CDIP,SBDIP,CSOP) 或 Pin13 (CLCC)           26         23         BD04         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           27         24         BD03         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           28         25         BD02         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           29         26         BD01         输入输出         参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           30         27         BD00         输入输出         券见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器           31         28         PL1         输入         并行加载输入信号: 加数第一个 16bit 字到发送器存储器           32         29         PL2         输入         并行加载输入信号: 加数第一个 16bit 字到发送器存储器           33         30         TV/R         输出         发送器数据输出           34         31         429DO         输出         发送器数据输出           35         32         429DO         输出         发送器数据输出           36         33         ENTX         输入         发达器被比解放通信号: 将控制字外从系统线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线线                                                                                                                                                                                                                                     | 22   | 19    | BD07  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 25     22     BD05     输入输出     参见 Pin11 (CDIP,SBDIP,CSOP) 或 Pin13 (CLCC)       26     23     BD04     输入输出     参见 Pin11 (CDIP,SBDIP,CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       27     24     BD03     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       28     25     BD02     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       29     26     BD01     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       30     27     BD00     输入输出     差別到2 (CLCC), 不能裁入数据到控制字寄存器       31     28     PL1     输入     并行加载输入信号; 加载第二个16bit 字到发送器存储器。并启动数据存输到存储器准线中       32     29     PL2     输入     并行加载输入信号; 加载第二个16bit 字到发送器存储器。并启动数据存输到存储器推线中       33     30     TX/R     输出     发送器备船出 发送器备船出       34     31     429DO     输出     发送器数据输出       35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器存储输入; 从 FIFO 存储器启动数据传输部                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23   | 20    | BD06  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 26       23       BD04       输入输出       参见 Pin11 (CDIP,SBDIP,CSOP) 或 Pin13 (CLCC),不能裁入数据到控制字寄存器         27       24       BD03       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC),不能裁入数据到控制字寄存器         28       25       BD02       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC),不能裁入数据到控制字寄存器         29       26       BD01       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC),不能裁入数据到控制字寄存器         30       27       BD00       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC),不能裁入数据到控制字寄存器         31       28       PL1       输入       并行加裁输入信号;加载第一个16bit 字到发送器存储器         32       29       PL2       输入       并行加裁输入信号;加载第一个16bit 字到发送器存储器         33       30       TX/R       输出       发送器数据输出         34       31       429DO       输出       发送器数据输出         35       32       429DO       输出       发送器数据输出         36       33       ENTX       输入       发送器数据输出         37       34       CWSTR       输入       发送器数定的输入; 从FIFO 存储器启动数据总线领存到控制字系         38       35       NC       -       不连接。         39       36       NC       -       不连接。         40       -       NC       -       不连接。 </td <td>24</td> <td>21</td> <td>GND</td> <td>输入</td> <td>地</td>                                                                                                                                                                                                                                                                          | 24   | 21    | GND   | 输入   | 地                                      |  |  |

| 26     23     BD04     輔入輸出     能裁入数据到控制字寄存器       27     24     BD03     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       28     25     BD02     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       29     26     BD01     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       30     27     BD00     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能裁入数据到控制字寄存器       31     28     PL1     输入     并行加裁输入信号: 加载第一个 16bit 字到发送器存储器       32     29     PL2     输入     并行加裁输入信号: 加载第一个 16bit 字到发送器存储器, 并启动数据存储器, 非启动数据存储器, 非启动数据存储器, 非启动数据存储器, 非启动数据存储器, 非启动数据传输       33     30     TX/R     输出     发送器数据输出       34     31     429DO     输出     发送器数据输出       35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器使能输入; 从 FIFO 存储器启动数据传输       37     34     CWSTR     输入     发送器使能输入; 从 FIFO 存储器启动数据连续领有到控制字寄存器       38     35     NC     -     不连接, 必须悬空或接地, 但不能接 Vcc       40     -     NC     -     不连接, 必须悬空或接地, 但不能接 Vcc       41     37     CLK     输入     网部时钟输入: 可以是 10 倍, 或 80 倍的数据速率。如果 使用 20 点面的数据速率。如果 20 点面的 2                                                                                                                                                                                                                                                                   | 25   | 22    | BD05  | 输入输出 | 参见 Pin11(CDIP,SBDIP,CSOP)或 Pin13(CLCC) |  |  |

| 27       24       BD03       輔入輸出       不能载入数据到控制字寄存器         28       25       BD02       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器         29       26       BD01       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器         30       27       BD00       输入输出       参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器         31       28       PL1       输入       并行加载输入信号: 加载第一个 16bit 字到发送器存储器 并启动数据传输器 并启动数据传输器 并启动数据传输器 并启动数据传输器 并启动数据传输器 并启动数据传输器 接触出 发送器 排输出 发送器 排输 计 发送器 扩充 从 发送器 推输出 发送器 排输出 发送器 排输 计 发送器 扩充 从 发送器 使能输入; 从 FIFO 存储器 启动数据传输 存器 中态 发展中态 大型 有器 全型 不连接, 必须悬空 或接地, 但不能接 Vcc         36       33       ENTX       输入 发送器 使能输入; 从 FIFO 存储器 启动数据传输 存器 中态 不连接, 必须悬空 或接地, 但不能接 Vcc         39       36       NC       -       不连接, 必须悬空 或接地, 但不能接 Vcc         40       -       NC       -       不连接, 必须悬空 或接地, 但不能接 Vcc         41       37       CLK       输入 同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。 如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。 典型值为 1MHz)         42       38       TXCLK       输出       发送器时钟输出: 提供的时钟频率等于发送器的数据速率。 单位信号: 低电平脉冲信号有效, 用于复位 FIFO、位计数据。 全有数据, TXR 和各种标志和控制信号。 不复位信号: 低电平脉冲信号有效, 用于复位等, TXR 和各种标志和控制信号。 不复位信号: 不复位信号: 不复位信号: 不复位信号: 不复位信号: 不复位信号: 不复位信号: 不复位信号: 不复位的特别, TXR 和各种标志和控制信息。 不复位的特别, TXR 和各种标志和控制信息。 不复位信号: 在电子联冲流 TXR 和各种标志和控制信息。 不复位的特别, TXR 和各种标志和控制信息。 不复位信号: 在电影器、 TXR 和各种标题, TXR 和各种标题, TXR 和各种标题, TXR 和各种标题, TXR 和各种M | 26   | 23    | BD04  | 输入输出 | , , , , , , , , , , , , , , , , , , ,  |  |  |

| 28     25     BD02     輔入輔出     不能载入数据到控制字寄存器       29     26     BD01     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器       30     27     BD00     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器       31     28     PL1     输入     并行加载输入信号: 加载第一个 16bit 字到发送器存储器       32     29     PL2     输入     并行加载输入信号: 加载第一个 16bit 字到发送器存储器, 并启动数据传输到存储器堆栈中       33     30     TX/R     输出     发送器输出就绪标志:表示发送器存储器空       34     31     429DO     输出     发送器数据输出       35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器数据输出       37     34     CWSTR     输入     控制字输入选通信号: 将控制字从数据总线锁存到控制字寄存器中       38     35     NC     -     不连接,必须悬空       39     36     NC     -     不连接,必须悬空       40     -     NC     -     不连接,必须悬空或接地,但不能接 Vcc       41     37     CLK     输入     对部时转输入:可以是 10 倍,或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。典型值为 1MHz)       42     38     TXCLK     输出     发送器时转输出:提供的时转频率等于发送器的数据速率。并定位信号: 低电平脉冲信号有效,用于复位 FIFO、位计数器。同隔计时器。字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                     | 27   | 24    | BD03  | 输入输出 |                                        |  |  |

| 29     26     BD01     输入输出     不能载入数据到控制字寄存器       30     27     BD00     输入输出     参见 Pin11 (CDIP, SBDIP, CSOP) 或 Pin13 (CLCC), 不能载入数据到控制字寄存器       31     28     PL1     输入     并行加载输入信号: 加载第一个 16bit 字到发送器存储器 并启动数据传输器工作中的转子储器工作中的转子储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器全       32     29     PL2     输入     并行加载输入信号: 加载第二个 16bit 字到发送器存储器,并启动数据传输器工作中的数据传输器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作的数据存储器工作的数据存储器工作的数据存储器工作中的数据存储器工作的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储的数据存储的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据存储器工作中的数据文字。如果有时使用ARINC数据注案必须是 10 倍最高的数据速率。如果有时使用ARINC数据速率必须是 10 倍最高的数据速率。如果有时使用ARINC数据速率必须是 10 倍最高的数据速率。如果有时使用ARINC数据速率必须是 10 倍最高的数据速率。如果有时的用为MRINC数据速率必须是 10 倍最高的数据速率。如果有时使用ARINC数据速率必须是 10 倍最高的数据速率。由于数据,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28   | 25    | BD02  | 输入输出 |                                        |  |  |

| 30     27     BD00     桐入棚田     不能载入数据到控制字寄存器       31     28     PL1     输入     并行加载输入信号: 加载第一个 16bit 字到发送器存储器       32     29     PL2     输入     并行加载输入信号: 加载第二个 16bit 字到发送器存储器,并启动数据传输到存储器堆栈中       33     30     TX/R     输出     发送器输出就绪标志:表示发送器存储器空       34     31     429DO     输出     发送器数据输出       35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器使能输入:从FIFO 存储器启动数据传输       37     34     CWSTR     输入     控制字输入选通信号: 将控制字从数据总线锁存到控制字寄存器中存器中分析的       38     35     NC     不连接,必须悬空       39     36     NC     不连接,必须悬空或接地,但不能接 Vcc       40     NC     不连接,必须悬空或接地,但不能接 Vcc       41     37     CLK     输入     内时使用 ARINC 数据速率必须是 10 倍最高的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。如果同时使用 ARINC 数据速率少须是 10 倍最高的数据速率。更值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29   | 26    | BD01  | 输入输出 |                                        |  |  |

| 32   29   PL2   输入                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30   | 27    | BD00  | 输入输出 |                                        |  |  |

| 32     29     PL2     输入     并启动数据传输到存储器堆栈中       33     30     TX/R     输出     发送器输出就绪标志:表示发送器存储器空       34     31     429DO     输出     发送器数据输出       35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器使能输入:从FIFO 存储器启动数据传输       37     34     CWSTR     输入     控制字输入选通信号:将控制字从数据总线锁存到控制字寄存器中       38     35     NC     -     不连接,必须悬空       39     36     NC     -     不连接,必须悬空或接地,但不能接 Vcc       40     -     NC     -     不连接。       41     37     CLK     输入     财命时钟输入:可以是 10 倍,或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31   | 28    | PL1   | 输入   | 并行加载输入信号:加载第一个 16bit 字到发送器存储器          |  |  |

| 34     31     429DO     输出     发送器数据输出       35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器使能输入:从FIFO 存储器启动数据传输       37     34     CWSTR     输入     控制字输入选通信号:将控制字从数据总线锁存到控制字寄存器中       38     35     NC     -     不连接,必须悬空       39     36     NC     -     不连接,必须悬空或接地,但不能接 Vcc       40     -     NC     -     不连接。       41     37     CLK     输入     同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32   | 29    | PL2   | 输入   |                                        |  |  |

| 35     32     429DO     输出     发送器数据输出       36     33     ENTX     输入     发送器使能输入:从FIFO 存储器启动数据传输       37     34     它WSTR     输入     控制字输入选通信号:将控制字从数据总线锁存到控制字寄存器中       38     35     NC     -     不连接,必须悬空       39     36     NC     -     不连接,必须悬空或接地,但不能接 Vcc       40     -     NC     -     不连接。       41     37     CLK     输入     同时使用 ARINC 数据速率必须是 10 倍,或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33   | 30    | TX/R  | 输出   | 发送器输出就绪标志:表示发送器存储器空                    |  |  |

| 36     33     ENTX     输入     发送器使能输入: 从 FIFO 存储器启动数据传输       37     34      控制字输入选通信号: 将控制字从数据总线锁存到控制字寄存器中       38     35     NC     - 不连接,必须悬空       39     36     NC     - 不连接,必须悬空或接地,但不能接 Vcc       40     - NC     - 不连接。       41     37     CLK     输入     如部时钟输入:可以是 10 倍,或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。典型值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出: 提供的时钟频率等于发送器的数据速率。主复位信号: 低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34   | 31    | 429DO | 输出   | 发送器数据输出                                |  |  |

| 37     34      控制字输入选通信号: 将控制字从数据总线锁存到控制字寄存器中       38     35     NC     -     不连接,必须悬空       39     36     NC     -     不连接,必须悬空或接地,但不能接 Vcc       40     -     NC     -     不连接。       41     37     CLK     输入     分部时钟输入:可以是 10 倍,或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35   | 32    | 429DO | 输出   | 发送器数据输出                                |  |  |

| 37     34     CWSTR     输入     存器中       38     35     NC     -     不连接,必须悬空或接地,但不能接 Vcc       39     36     NC     -     不连接,必须悬空或接地,但不能接 Vcc       40     -     NC     -     不连接。       41     37     CLK     输入     期入     同时使用 ARINC 数据速率必须是 10 倍最高的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)       42     38     TXCLK     输出     发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36   | 33    | ENTX  | 输入   | 发送器使能输入:从 FIFO 存储器启动数据传输               |  |  |

| 39       36       NC       -       不连接,必须悬空或接地,但不能接 Vcc         40       -       NC       -       不连接。         41       37       CLK       输入       外部时钟输入:可以是 10 倍,或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)         42       38       TXCLK       输出       发送器时钟输出:提供的时钟频率等于发送器的数据速率。主复位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37   | 34    | CWSTR | 输入   |                                        |  |  |

| 40       -       NC       -       不连接。         41       37       CLK       输入       外部时钟输入: 可以是 10 倍, 或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)         42       38       TXCLK       输出       发送器时钟输出: 提供的时钟频率等于发送器的数据速率。主复位信号: 低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38   | 35    | NC    | -    | 不连接,必须悬空                               |  |  |

| 41       37       CLK       输入       外部时钟输入: 可以是 10 倍, 或 80 倍的数据速率。如果同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)         42       38       TXCLK       输出       发送器时钟输出: 提供的时钟频率等于发送器的数据速率。主复位信号: 低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39   | 36    | NC    | -    | 不连接,必须悬空或接地,但不能接 Vcc                   |  |  |

| 41       37       CLK       输入       同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典型值为 1MHz)         42       38       TXCLK       输出       发送器时钟输出:提供的时钟频率等于发送器的数据速率。         43       39       面       输入       单位信号:低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40   | _     | NC    | -    | 不连接。                                   |  |  |

| 全复位信号: 低电平脉冲信号有效,用于复位 FIFO、位计数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41   | 37    | CLK   | 输入   | 同时使用 ARINC 数据速率必须是 10 倍最高的数据速率(典       |  |  |

| 43 39 MR 输入 数器,间隔计时器,字计数器,TX/R 和各种标志和控制信号。不复位控制字寄存器。通常只用在上电或系统复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42   | 38    | TXCLK | 输出   | 发送器时钟输出:提供的时钟频率等于发送器的数据速率。             |  |  |

| 44 40 NC - 不连接                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43   | 39    | MR    | 输入   | 数器,间隔计时器,字计数器,TX/R 和各种标志和控制信           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44   | 40    | NC    | -    | 不连接                                    |  |  |

## 3.3 功能描述

GY3282 不仅支持 ARINC 429 规范的要求,还支持其他使用类似格式的串行数据协议(在单个低功耗 LSI 集成电路上实现接收、发送、同步、定时和奇偶校验功能)。它超出了 ARINC 的要求,提供奇偶校验,并支持 25 或 32 位字长。在总线接口电路中,接收器和发送器部分各自独立工作,接收器实现了串并转换功能,发送器实现了并串转换功能,通过一个 10 倍于数据速率的外部时钟输入,提供灵活的数据速率。

GY3282 通过一些外部控制信号可以实现上述的灵活性,通过使用内部控制字寄存器减少引脚数量。 控制字选通信号(CWSTR)输入为逻辑"1"时,控制字从数据总线锁存到寄存器中。

GY3282 提供了 11 种控制功能,与总线数据线并列如下:

| 引脚名         | 符号     | 功能描述                                                                                                  |

|-------------|--------|-------------------------------------------------------------------------------------------------------|

| BD05        | SLFTST | 自测试使能位,若 SLFTST = "0",则启动自检功能。绕过输入接收器,将自测信号从发送器直接连接到接收器移位寄存器。接收器 1 接收同向数据,接收器 2 接收反向数据。注意,发送器的输出保持有效。 |

| BD06        | SDENB1 | 接收器 1 源/目标代码检验使能位, "1"使能, "2"禁止。                                                                      |

| BD07        | X1     | 若 SDENB1 = "1" ,则该位数据与 ARINC 数据位#9 比较。如果 Y1 同时相同(参看 Y1),<br>该数据字会被接收通道 1 接收。若 SDENB1 = "0" ,则忽略该 bit。 |

| BD08        | Y1     | 若 SDENB1 = "1",则该位数据与 ARINC 数据位#10 比较。如果 X1 同时相同(参看 X1),该数据字会被接收通道 1 接收。若 SDENB1 = "0",则忽略该 bit。      |

| BD09        | SDENB2 | 接收器 2 源/目标代码检验使能位, "1"使能, "2"禁止。                                                                      |

| BD10        | X2     | 若 SDENB2 = "1" ,则该位数据与 ARINC 数据位#9 比较。如果 Y2 同时相同(参看 Y2),该数据字会被接收通道 2 接收。若 SDENB2 = "0" ,则忽略该 bit。     |

| BD11        | Y2     | 若 SDENB1 = "1",则该位数据与 ARINC 数据位#10 比较。如果 X2 同时相同(参看 X2),该数据字会被接收通道 2 接收。若 SDENB1 = "0",则忽略该 bit。      |

| BD12        | PARCK  | 校验位检查。逻辑"0"选择奇校验,逻辑"1"选择偶校验。                                                                          |

| BD13        | TXSEL  | 发送器速率选择。若 TXSEL = "0",则发送数据速率=时钟频率/10;若 TXSEL = "1",则<br>发送数据速率 = 时钟频率/80。                            |

| BD14 RCVSEL |        | 接收器速率选择。若 RCVSEL = "0",则接收送数据速率=时钟频率/10;若 RCVSEL = "1",则接收数据速率 = 时钟频率/80。                             |

| BD15        | WLSEL  | 字长度选择。若 WLSEL = "0" ,则支持数据字长为 32bit;若 WLSEL = "1" ,则支持数据字长为 25bit。                                    |

#### 3.3.1 ARINC 429 的数据格式如下(接收器的输入和发送器的输出):

a) 当采用 32 位数据字长时, 其数据格式如下所示:

ARINC 32BIT 数据格式

| ARINC BIT # | 功能          |  |

|-------------|-------------|--|

| 1 ~ 8       | Label       |  |

| 9 ~ 10      | SDI or Data |  |

| 11          | LSB         |  |

| 12 ~ 27     | Data        |  |

| 28          | MSB         |  |

| 29          | Sign        |  |

| ARINC BIT # | 功能            |

|-------------|---------------|

| 30, 31      | SSM           |

| 32          | Parity Status |

这种格式会变为下面的格式:

WORD1 格式

| BI-DIRECTIONAL BIT # | FUNCTION      | ARINC BIT # |  |  |

|----------------------|---------------|-------------|--|--|

| 15, 14               | Data          | 13, 12      |  |  |

| 13                   | LSB           | 11          |  |  |

| 12, 11               | SDI or Data   | 10, 9       |  |  |

| 10, 9                | SSM Status    | 31, 30      |  |  |

| 8                    | Parity Status | 32          |  |  |

| 7 ~ 0                | Label         | 1 ~ 8       |  |  |

WORD2 格式

| BI-DIRECTIONAL BIT # | FUNCTION | ARINC BIT # |  |  |

|----------------------|----------|-------------|--|--|

| 15                   | Sign     | 29          |  |  |

| 14                   | MSB      | 28          |  |  |

| 13 ~ 00              | Data     | 27 ~ 14     |  |  |

接收器的奇偶校验位状态: "0" = 奇校验, "1" = 偶校验。

如果在接收器接收完整个数据字之前,接收器输入的数据字串被打断,则接收器将重置并忽略部分接收到的数据字。

如果发送器传输连续的数据字,每个字将被一个 4 位的 "null"状态分隔(正输出和负输出都将保持 0 电平)。

b) 当采用 25 位字长时, 其数据格式如下所示:

ARINC 25BIT 数据格式

| ARINC BIT # | FUNCTION      |  |

|-------------|---------------|--|

| 1 ~ 8       | Label         |  |

| 9           | LSB           |  |

| 11 ~ 23     | Data          |  |

| 24          | MSB           |  |

| 25          | Parity Status |  |

这种格式会变为下面的格式,其中数据 1 的格式为:

WORD1 格式

| BI-DIRECTIONAL BIT # | FUNCTION      | ARINC BIT # |  |

|----------------------|---------------|-------------|--|

| 15 ~ 9               | Don't Care    | XXX         |  |

| 8                    | Parity Status | 25          |  |

| 7 ~ 0                | Label         | 1 ~ 8       |  |

数据 2 的格式为:

#### WORD2 格式

| BI-DIRECTIONAL BIT # | FUNCTION | ARINC BIT # |  |

|----------------------|----------|-------------|--|

| 15                   | MSB      | 24          |  |

| 14 ~ 1               | Data     | 23 ~ 10     |  |

| 0                    | LSB      | 9           |  |

接收器的奇偶校验位状态: "0" = 奇校验, "1" = 偶校验。

25 位字长数据格式没有 S/D 解码器。

#### 3.3.2 接收器功能

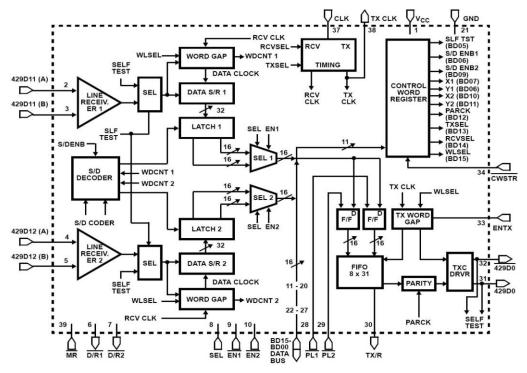

由于两个接收器在功能上是相同的,因此这里只对其中一个进行详细描述,以图 3 内部框图为参考。接收器由以下电路组成:

#### a) Line Receiver:

线路接收器的功能是将 10V 差分总线数据格式转换为 5V 内部逻辑电平。

#### b) Self-Test Data Selector (SEL)

线路接收器的输出是自测试数据选择器(SEL)的两个输入之一。数据选择器的另一个输入是来自发送器部分的自测信号。

#### c) Word Gap Timer

输入数据(自测试数据或总线数据)由字间隔定时器进行双重采样,以生成数据时钟。接收器采样频率为 1MHz 或 125kHz,由接收器/发送器时序电路产生。该采样频率是数据速率的十倍,以确保所有的数据都被正确采样。

#### d) Data Shift Register (Data S/RI)

产生的数据时钟将数据移到一个 32 位长的数据移位寄存器(Data S/RI)。数据字的长度通过控制寄存器的 WLSEL 选择为 25 位或 32 位。当数据完整接收后,字间隔计时器会产生一个内部信号(WDCNT1)。

### e) Source/Destination (S/D) Decoder

S/D解码电路比较用户设置字(X和 Y)和数据位 9 和 10。如果两个码都匹配,会产生一个高电平使能信号 WDCNT1 锁存数据到接收缓冲器;否则,该数据会被忽略,不会被锁存。S/D 解码电路通过设置控制字 S/D ENB 来启用和禁用。当数据被锁存后,会产生指示信号 $\overline{D/R1}$ ,该信号表明数据已经准备好。

- f) 当接收数据被移位到移位寄存器后,会放入到保持寄存器中。然后产生一个设备就绪标志,表明数据已经准备好可以提取了。如果数据被忽略并存放在保存寄存器中,则在接收到下一个数据字时将其重写。

- g)保持寄存器接收到的数据以两个16bit字的形式输出到数据总线上(无论数据格式是32bit还是25bit)。直到下个数据被写入保持寄存器之前,数据可以一直被读取。

- h)输入数据要进行奇偶校验(逻辑"0"为奇校验,逻辑"1"为偶校验),结果会保存在接收锁存器中,在第一个接收数据字被校验的期间,通过BD08输出。

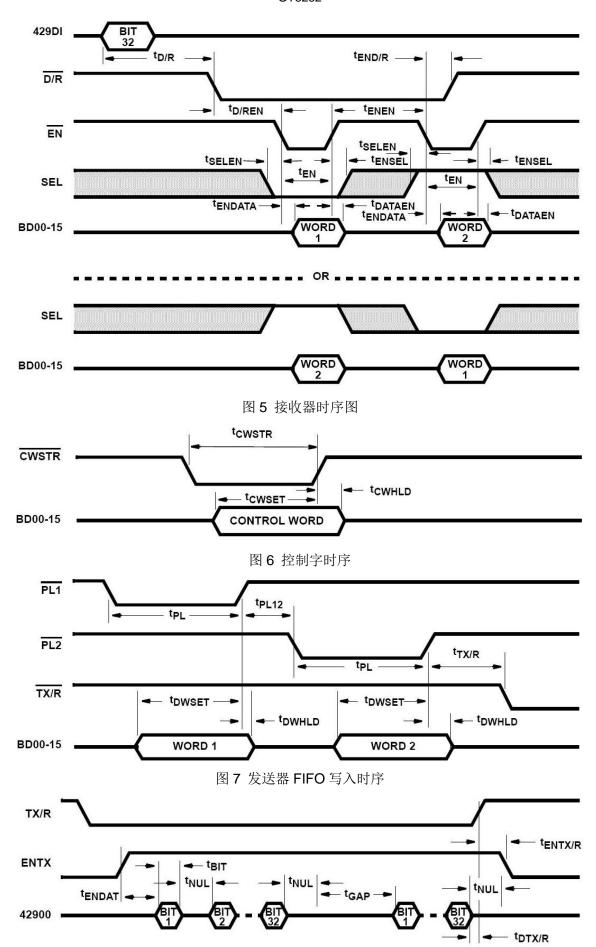

- i)为了读取接收器数据,用户需设置接收器数据选择信号(SEL)为"0",并将输出使能端(EN1) 拉低,WORD1被放到数据总线上。为了读取WORD2,用户需设置接收器数据选择信号(SEL)为"1"

并将输出使能端(EN1)拉低,WORD2放到数据总线上。使能脉冲持续时间与从数据总线读取数据字所需的电路要求相匹配。第二个使能脉冲也用于重置 D/R1 触发器,完成了一个接收数据周期。

#### 3.3.3 发送器功能

GY3282 的发送部分由 8 个 31bits 的 FIFO、奇偶校验位生成电路、发送 Word Gap 电路以及驱动电路构成。

#### a) FIFO Memory

该 FIFO 的工作方式:加载在输入寄存器中的数据自动传输到串行数据传输输出寄存器。这消除了大量的数据管理时间,因为数据从输入寄存器到输出寄存器不需要计时。FIFO 的输入寄存器由两个分别被 PL1和PL2控制的 D 触发器组成,PL1必须先于PL2产生。多个PL1会导致数据被覆盖。当PL2产生后,数据会传送至 FIFO。数据总线上的信号会在 PL 信号的上升沿被采样至 D 触发器。如果 FIFO 为空,或者 FIFO 堆栈没有写满,数据会自动传送至存储堆栈到输出寄存器或者最后一个空的 FIFO 寄存器。

若发送使能信号(ENTX)为"0",数据会保持在输出寄存器。该 FIFO 可以保存 8 个 31bit 字。如果 FIFO 已满,并且 PL 信号指示新的数据到来,输入寄存器内的数据会被新的数据覆盖。数据会继续保存在存储中直至 ENTX 为"1"。

当 ENTX 为 1 后,会使能 FIFO 的时钟,并且将数据串行输出至发送驱动器。只有当 ENTX 为 "0"时,数据才能加载到 FIFO。在发送使能时向 FIFO 写入数据是被禁止的。(当 ENTX 为 "1"时,若 PL1 或 PL2 有效会导致 FIFO 混乱,只能通过 MR 信号复位)

#### b) Output Register of the FIFO

FIFO 的输出寄存器被设计为通过 WLSEL 控制,可以移位 24bit 数据或者 31bit 数据。TX 字间隔计时器电路在两个数据字之间插入 4bit 时间的间隔。这就使发送电路发送一个数据字的最小时间为 29bit 时间或 36bit 时间。假设 ENTX 信号保持为"1",会产生控制信号将数据从存储堆栈中移出,直至最后一个字从 FIFO 中移出。此时,会产生发送准备好状态指示信号(TX/R)告知用户发送电路已经准备好接收另外8个数据字。在发送期间,如果 ENTX 被拉低然后变高,发送将被中止并且有一部分数据未被发送,FIFO的数据完整性会被破坏。

### c) Bit Counter

位计数器用于判定最后的数据位移出 FIFO 并插入奇偶校验位。奇偶校验位生成电路通过 PARCK 电路来控制, PARCK 电路决定输出数据字是使用奇偶校验还是奇偶校验。PARCK 为"0"时将插入奇校验位,为"1"时插入偶校验位。

#### 3.3.4 接口技术示例

由于数据总线被发送电路和接收电路复用,因此,总线控制必须在发送电路和接收电路中同步。

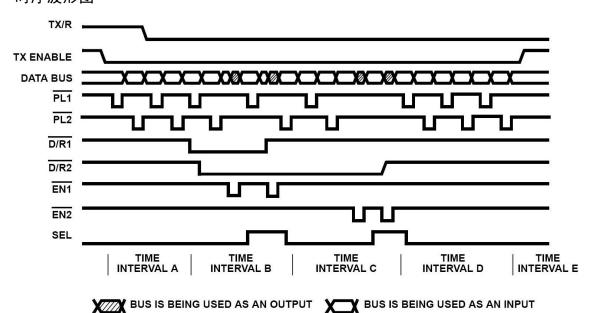

图 4 给出了 GY3282 收发控制的时序图。加载发送器 FIFO 的时序如图中的 TIME INTERVAL A 所示。 发送器准备就绪标志(TX/R)有效表明发送存储已空。此时可以数据总线上发送一个 16 位字数据,并通过并行加载信号(PL1)选通发送器。32 位字的第二部分同样用PL2 加载到发送器,同时,它也开始向堆栈传输数据。这是连续的,直到内存被填满,也就是 8 个 31 位字。用户必须控制加载到内存中的字数,版本: V1.0

以确保没有数据被其他数据重写。当用户载入发送数据时,即使D/R1信号表明接收数据已经准备好,用户也无需去响应,如时序图中的 TIME INTERVAL B 所示。如果用户决定在发射器完全加载之前获取接收到的数据,两个并行加载信号(PL1和PL2)要设置为逻辑"1",当 SEL 为逻辑"0"时,产生EN1选通脉冲。在EN1的下降沿之后,接收到的第一个 16 位数据在数据总线上生效。在EN1的上升沿,需要切换信号 SEL,去接收第二个 16 位数据。通过EN1脉冲选通接收器,启用第二个 16 位字,并重置接收器就绪标志 D/R1。将 SEL 信号重置为逻辑"0"以使接收端准备下一个读周期。在获取接收数据时,可以载入发送数据,通过将 PL信号以及 EN信号变成 TIME INTERVAL B 中所示的状态即可实现。TIME INTERVAL C 给出了接收器 2 中的相关时序控制,与接收器 1 类似。TIME INTERVAL D 给出了发送器加载序列的其余部分,以及通过将信号 TX 使能切换到逻辑"1"状态以开始发送数据。当 TXEN 为 1 后,数据开始发送。TIME INTERVAL E 是从 FIFO 内存传输所有数据所需的时间,可以是 288 位时长,也可以是 232 位时长。3.3.5 中继器操作

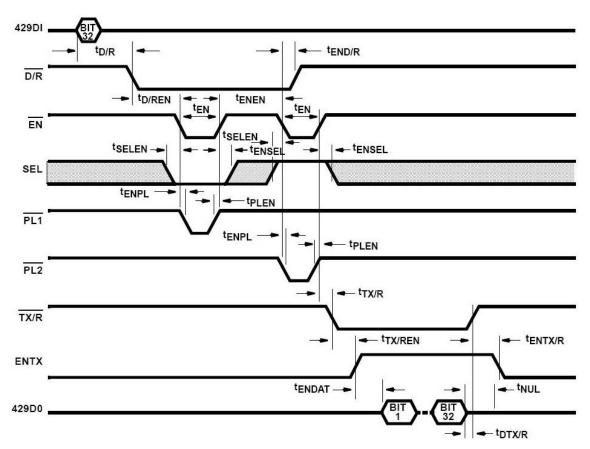

这种操作模式允许将接收到的数据字直接放置在 FIFO 中进行传输。时序如图 9 所示。本例中使用了一个 32 位字长,数据字被移到移位寄存器中, D/R1标志有效输出 "0"。当 SEL 为逻辑 "0"时,产生EN1选通脉冲,这与普通的接收操作相同,将一半的数据字(16 位)放在数据总线上。在EN1有效的同时选通 PL1,这 16 位数据字将被从总线上取下并放置在 FIFO 中。对于数据字的第二个 16 位数据字,当 SEL 为逻辑 "1"时,再次产生EN1选通脉冲。在EN1有效的同时选通PL2,这数据的第二个 16 位数据字被放置在 FIFO 中。奇偶校验位将被剥离,留下 FIFO 中的 31 位数据字准备传输,如图 8 所示。

### 3.4 工作原理框图

图 3 工作原理框图

# 3.5 绝对最大额定值<sup>[1]</sup>

| 电源电压                                                | +7.0V                                  |

|-----------------------------------------------------|----------------------------------------|

| 输入、输出或 I/O 电压(Pin2 ~ Pin5 除外) ······                | ··· GND-0.3V ~ (V <sub>DD</sub> +0.3V) |

| 输入电压 (Pins 2 ~ 5) ······                            |                                        |

| ESD 等级 ······                                       | 2 级 (2000V ≤ ESD ≤ 3999V)              |

| 工作温度                                                |                                        |

| 最大存储温度                                              |                                        |

| 最大引脚温度(焊接 10s) ···································· | +300°C                                 |

注 $^{[1]}$ :在"绝对最大额定值"中列出的是器件正常工作的额定值,并未涉及器件在这些条件或超出这些条件下的功能操作。 器件不能长时间工作在绝对最大额定值条件下,否则会影响其可靠性和对器件造成永久损害。

## 3.6 参数列表

**直流电性能指标**(除非另有说明,V<sub>DD</sub> = 5V±5%,-55°C ≤ T<sub>A</sub> ≤ +125°C)

| 参数                                 | 符号                                                            | 测试条件                                                                                    | 最小值   | 最大值  | 单位 |

|------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|----|

| ARINC 输入引脚 Pin2~Pin3、Pin4~Pin5     |                                                               |                                                                                         | •     |      |    |

| 逻辑"1"输入电压                          | $V_{IH}$ $V_{DD} = 5.25V$                                     |                                                                                         | 6.7   | 13.0 | V  |

| 逻辑"0"输入电压                          | V <sub>IL</sub>                                               | V <sub>DD</sub> = 5.25V                                                                 | -13.0 | -6.7 | V  |

| "Null"输入电压                         | V <sub>NUL</sub>                                              | V <sub>DD</sub> = 4.75V, 5.25V                                                          | -2.5  | +2.5 | V  |

| 共模电压范围                             | V <sub>CH</sub>                                               | V <sub>DD</sub> = 4.75V, 5.25V                                                          | -5.0  | +5.0 | V  |

| 输入漏电流                              | I <sub>IH</sub>                                               | $V_{DD} = 5.25V, V_{IN} = \pm 6.5V$                                                     | -     | 200  | μΑ |

| 输入漏电流                              | I <sub>IL</sub>                                               | $V_{DD} = 5.25V, V_{IN} = 0.0V$                                                         | -450  | _    | μΑ |

| 差分输入阻抗                             | RI                                                            | $V_{DD} = 5.25V, V_{IN} = +5V, -5V$                                                     | 12    | -    | kΩ |

| 输入到 V <sub>DD</sub> 阻抗             | RH                                                            | $V_{DD} = 5.25V, V_{IN} = 0.0V$                                                         | 12    | -    | kΩ |

| 输入到 GND 阻抗                         | RG                                                            | $V_{DD} = Open, V_{IN} = 5.0V$                                                          | 12    | -    | kΩ |

| 双向输入引脚 Pin11 ~ Pin20、Pin22 ~ Pin27 |                                                               |                                                                                         |       |      |    |

| 逻辑"1"的输入电压                         | V <sub>IH</sub>                                               | V <sub>DD</sub> = 5.25V                                                                 | 2.1   | -    | V  |

| 逻辑"0"的输入电压                         | V <sub>IL</sub>                                               | V <sub>DD</sub> = 4.75V                                                                 | -     | 0.7  | V  |

| 输入漏电流                              | I <sub>IH</sub>                                               | $V_{DD} = 5.25V$ , $V_{IN} = 5.25V$                                                     | -     | 1.5  | μΑ |

| 输入漏电流                              | I <sub>IL</sub>                                               | $V_{DD} = 5.25V, V_{IN} = 0.0V$                                                         | -1.5  | _    | μΑ |

| 其他输入引脚 Pin8 ~ Pin 10、Pin28、Pin 29、 | Pin 33、Pin                                                    | 34、Pin 37、Pin 39                                                                        |       |      |    |

| 逻辑"1"的输入电压                         | V <sub>IH</sub>                                               | V <sub>DD</sub> = 5.25V                                                                 | 3.5   | -    | V  |

| 逻辑"0"输入电压                          | V <sub>IL</sub>                                               | V <sub>DD</sub> = 4.75V                                                                 | -     | 0.7  | V  |

| 输入漏电流                              | I <sub>IH</sub>                                               | $V_{DD} = 5.25V$ , $V_{IN} = 5.25V$                                                     | _     | 10   | μΑ |

| 输入漏电流                              | I <sub>IL</sub>                                               | $V_{DD} = 5.25V, V_{IN} = 0.0V$                                                         | -75   | -    | μΑ |

| 输出引脚 Pin6、Pin7、Pin11~Pin20、Pin22   | 俞出引脚 Pin6、Pin7、Pin11~Pin20、Pin22~Pin27、Pin30~Pin32、Pin38、Pin1 |                                                                                         |       |      |    |

| 逻辑"1"的输出电压                         | V <sub>OH</sub>                                               | $V_{DD} = 4.75V$ , $I_{OH} = -1.5mA$                                                    | 2.7   | -    | V  |

| 逻辑 "0" 的输出电压                       | V <sub>OL</sub>                                               | $V_{DD} = 4.75V, I_{OL} = 1.8mA$                                                        | -     | 0.4  | V  |

| 待机电流                               | I <sub>CC1</sub>                                              | $V_{DD} = 5.25V, V_{IN} = 0V$ (除了 Pin9,Pin10,Pin29=5.25V)                               | _     | 20   | mA |

| 工作电流                               | I <sub>CC2</sub>                                              | V <sub>DD</sub> = 5.25V,V <sub>IN</sub> = 5.25V<br>(除了 Pin8,Pin33 = 0.0V)<br>CLK = 1MHz | -     | 20   | mA |

# **交流电性能指标**(除非另有说明, $V_{DD}$ = $5V\pm5\%$ ,- $55^{\circ}C \le T_{A} \le +125^{\circ}C$ )

| 时钟頻率                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 参数                                  | 符号                              | 测试条件                           | 最小值   | 最大值   | 单位  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------|--------------------------------|-------|-------|-----|--|--|--|

| 数形速率   FD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 时钟频率                                | FC                              | $V_{DD} = 4.75V, 5.25V$        | _     | 1     | MHz |  |  |  |

| 主要位脉中度度                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 数据速率 <sup>[1]</sup>                 | FD                              | $V_{DD} = 4.75V, 5.25V$        | -     | 100   | kHz |  |  |  |